Интернет магазин китайских планшетных компьютеров |

|

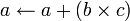

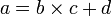

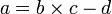

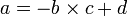

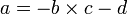

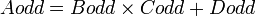

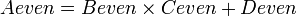

Компьютеры - Умножение-сложение23 января 2011В вычислительной технике, особенно в цифровой обработке сигналов совмещённое умножение-сложение — распространённая операция, при которой умножаются два числа и складываются с аккумулятором. Когда операция выполняется над числами с плавающей запятой, то может выполняться двойное округление или однократное. Версия с однократным округлением также называется fused multiply-add или fused multiply-accumulate. НазначениеДанная инструкция позволяет более эффективно реализовать операции деления и извлечения квадратного корня, умножение векторов и матриц, вычисление полиномов по схеме Горнера. Реализация в процессорахОперация включена в стандарт IEEE 754-2008. В стандарт 1999 года на язык программирования Си включена поддержка операции FMA из math.h). Современные компьютеры могут иметь специализированный блок умножения-сложения или MAC, состоящий из умножителя реализующего комбинационную логику и сумматора, а также аккумулятора, в котором сохраняется результат. Выход аккумулятора подаётся на один из входов сумматора, и таким образом каждый такт результат из умножителя складывается с аккумулятором. Реализация MAC требует дополнительной логики на кристалле, но вычисления происходям быстрее, чем при использовании метода сдвигов и сложений типичного для первых компьютеров. Появившись на сигнальных процессорах, операция включена в системы команд процессоров: IBM POWER1, Fujitsu SPARC64, HP PA-8000, Sony Emotion Engine, Intel Itanium, IBM Cell. Также она будет реализована в процессорах AMD с поддержкой FMA4. Intel планирует добавить FMA3 в процессоры на ядре Haswell к 2012. Технология присутствует в NVIDIA GPU серий GeForce 200, GeForce 300 и NVIDIA Tesla GPGPU C1060 & C2050 / C2070. AMD добавила FMA в линию Radeon с серии HD 5000. Инструкции FMA, реализованные в процессорах Intel Sandy Bridge:

Просмотров: 1584

|