Интернет магазин китайских планшетных компьютеров |

|

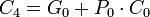

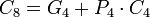

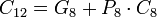

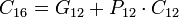

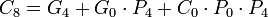

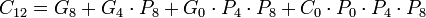

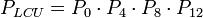

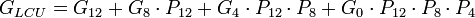

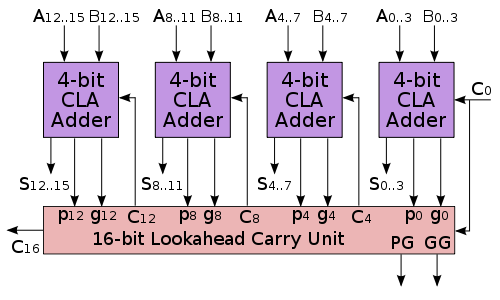

Компьютеры - Схема ускоренного переноса - 16-ти битная схема23 января 2011Оглавление: 1. Схема ускоренного переноса 2. 16-ти битная схема 3. 64-битная схема 16-разрядный сумматор может быть создан путём объединения четырёх 4-битных сумматоров с четырьмя схемами ускоренного переноса, дополненных пятой схемой ускоренного переноса, которая используется для обработки групповых сигналов генерации переноса — GG и распространения переноса — PG. Принимаемые на входе сигналы распространения переноса и генерируемые каждой их четырёх схем сигналы. Затем, схема ускоренного переноса генерирует соответствующие сигналы. Предположим, что Pi это сигналы PG и Gi это GG из i, то выходные биты устанавливаются следующим образом: Подставляя C4 сперва в C8, затем C8 в C12, затем C12 в C16 получаем следующее расширение выражения: C4 соответственно генерирует бит переноса на вход второй схемы; C8 на вход третьей; C12 на вход четвёртой; и C16 генерирует бит переполнения. Кроме того, можно вычислить сигналы распространения переноса и генерации переноса для схемы ускоренного переноса:

16-разрядный сумматор со схемой ускоренного переноса

Просмотров: 3592

|