|

|

|

27 апреля 2011

Оглавление:

1. NetBurst

2. Описание работы

3. Особенности архитектуры

4. Процессоры архитектуры NetBurst

NetBurst — суперскалярная гиперконвейерная микроархитектура, разработанная компанией Intel и лежавшая в основе микропроцессоров Pentium 4, Pentium D, Celeron и Xeon. Архитектура NetBurst пришла на смену архитектуре P6 на рынке настольных и серверных процессоров. Она не являлась развитием архитектуры P6, а представляла собой принципиально новую по сравнению со всеми предшественниками архитектуру. Первые процессоры архитектуры NetBurst были анонсированы 20 ноября 2000 года, а 8 августа 2007 года компания Intel объявила о начале действия программы по снятию с производства всех процессоров этой архитектуры. На смену процессорам архитектуры NetBurst пришли процессоры семейства Core 2 Duo, архитектура которых представляет собой развитие архитектуры P6.

Описание функциональных блоков

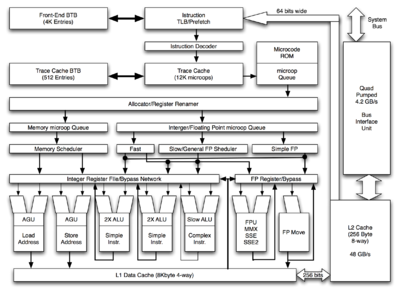

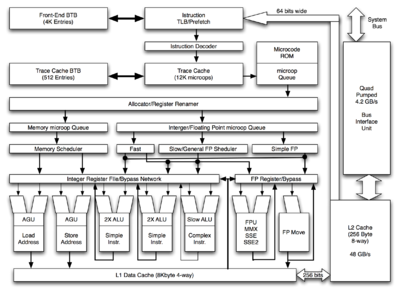

Функциональная схема процессора Pentium 4 на ядре Willamette

Процессоры архитектуры NetBurst состоят из четырёх основных структурных блоков:

- Исполнительные устройства, осуществляющие выполнение инструкций, а также устройства, обеспечивающие взаимодействие исполнительных устройств.

- Входной блок, отвечающий за предвыборку данных, предсказание ветвлений и декодирование инструкций.

- Устройства организации внеочередного исполнения, обеспечивающие оптимальный порядок исполнения микроопераций.

- Интерфейс памяти, представляющий собой группу устройств, обеспечивающих взаимодействие процессора с подсистемой памяти.

Исполнительные устройства

К исполнительным устройствам относятся:

- Целочисленный регистровый файл и логика, обеспечивающая непосредственную передачу данных между блоками АЛУ. Регистровый файл обеспечивает хранение результатов операций, однако при этом данные могут передаваться между исполнительными блоками минуя регистровый файл.

- Блоки генерации адреса чтения и записи. Предназначены для взаимодействия с кэшем данных. Формируют адреса, по которым производятся операции чтения и записи.

- АЛУ. Осуществляют выполнение целочисленных операций.

- Целочисленный регистровый файл и логика, обеспечивающая непосредственную передачу данных между блоком обработки чисел с плавающей запятой, обеспечивающем выполнение инструкций x87, MMX, SSE и SSE2.

- Блоки обработки чисел с плавающей запятой. Осуществляют выполнение операций над вещественными числами, в том числе операции чтения и записи.

В процессорах на ядре Prescott и более новых блок обработки чисел с плавающей запятой получил поддержку инструкций SSE3.

Устройства организации внеочередного исполнения

Внеочередное исполнение позволяет ускорить работу за счёт изменения порядка выполнения микроопераций в тех случаях, когда это изменение не приведёт к изменению результата. К устройствам организации внеочередного исполнения относятся:

- Диспетчер ресурсов. Осуществляет распределение вычислительных ресурсов, переименование регистров, а также отслеживает состояние всех микроопераций, находящихся в обработке.

- Очереди микроопераций. Содержат микрооперации, которые необходимо выполнить. При этом микрооперации, осуществляющие взаимодействие с памятью, отделены от всех остальных и размещаются в специальной очереди.

- Планировщики микроопераций. Определяют готовность микроопераций, находящихся в очередях, к исполнению и направляют их на выполнение в соответствующие исполнительные блоки.

Устройства входного блока

К устройствам входного блока относятся:

- Модуль и буферы предсказания ветвлений. Осуществляют предсказание ветвлений и хранят таблицу истории переходов. Для предсказания ветвлений используется как динамический, так и статический методы. Последний используется в том случае, если динамическое предсказание невозможно.

- Кэш последовательностей микроопераций. Хранит последовательности микроопераций в соответствии с предполагаемым порядком их исполнения.

- Декодер инструкций. Осуществляет преобразование CISC-инструкций x86 в последовательность RISC-микроопераций, исполняемых процессором.

- Блок предвыборки инструкций. Осуществляет предварительную выборку инструкций на основании таблиц предсказания ветвлений и преобразование программного адреса инструкции в физический с помощью таблицы трансляции адресов.

- ПЗУ микрокода. Используется кэшэм последовательностей микроопераций при преобразовании сложных инструкций x86 в последовательность микроопераций.

- Очередь микроопераций. Содержит микрооперации, поступающие на конвейер процессора.

Интерфейс памяти

Интерфейс памяти осуществляет взаимодействие с оперативной памятью. К этому блоку относятся:

- Кэш-память данных первого уровня. Память объёмом 8 или 16 КБ с малым временем доступа.

- Кэш-память второго уровня. Память объёмом 128, 256, 512, 1024 или 2048 КБ с малым временем доступа. Соединяется с кэшем первого уровня шиной шириной 256 бит.

- Блок шинного интерфейса. Осуществляет управление системной шиной.

Некоторые процессоры содержали также кэш-память третьего уровня объёмом 2, 4 или 8 МБ.

Просмотров: 4776

|