Интернет магазин китайских планшетных компьютеров |

|

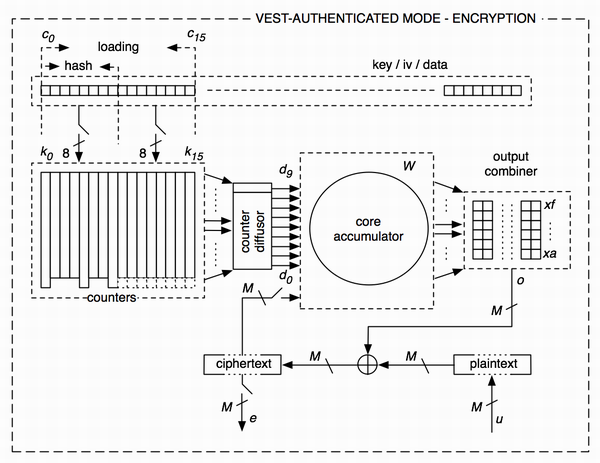

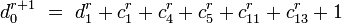

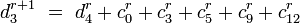

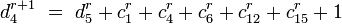

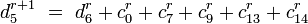

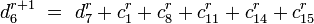

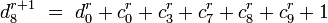

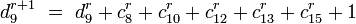

Компьютеры - VEST - Аппаратная реализация29 мая 2011Оглавление: 1. VEST 2. Аппаратная реализация 3. Режимы работы 4. Криптостойкость 5. Применение Общая структураСхема шифрования состоит из четырёх основных компонентов: нелинейный счетчик, линейный счетчик-диффузор, биективный накапливающий регистр с большим числом состояний и линейный смеситель на выходе. Ядро шифров VEST можно представить как взаимно-однозначные регистры сдвига с нелинейной обратной связью с множеством параллельных обратных связей, работающие вместе с системой нелинейных модульных счетчиков с очень длинным периодом. Модульный счетчик состоит из 16 регистров сдвига с нелинейной обратной связью с взаимно простыми длинами периодов. Счетчик-диффузор – это набор 6-битовых линейных смесителей с обратной связью, сжимающий выходные данные с 16 счетчиков в 10 бит. Ядро накапливающего регистра – регистр сдвига с нелинейной параллельной обратной связью, на вход которого подаются выходные 10 бит от счетчика-диффузора. Выходной смеситель – набор 6-битовых линейных смесителей. Счетчик-диффузорБиты, поступившие на вход счетчика-диффузора, смешиваются перед подачей их на вход накапливающего регистра по следующему правилу: Накапливающий регистр

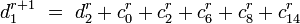

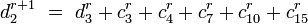

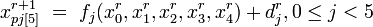

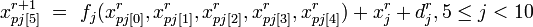

Младшие пять бит x0, x1, x2, x3, x4 преобразуются нелинейными функциями f0, f1, f2, f3, f4, которые образуют блок подстановки. Значения этих функций линейно смешиваются с пятью выходными битами d0, d1, d2, d3, d4 счетчика-диффузора и возвращаются обратно в состояние регистра в xp0, xp1, xp2, xp3, xp4 соответственно. Биты x5, x6, x7, x8, x9 линейно смешивают со значениями следующих пяти функций с обратной связью f5, f6, f7, f8, f9 и с пятью битами счетчика-диффузора d5, d6, d7, d8, d9 и возвращаются в состояние регистра в xp5, xp6, xp7, xp8, xp9 соответственно. Биты от x10 до xM + 9 линейно смешиваются с значениями функций f10,..., fM + 9, а в режиме шифрования с аутентификацией ещё и с битами шифротекста. Работу ядра накапливающего регистра можно изобразить с следующем виде:

Просмотров: 4087

|

;

; ;

; ;

;