Интернет магазин китайских планшетных компьютеров |

|

Компьютеры - Кэш процессора - Принцип работы23 января 2011Оглавление: 1. Кэш процессора 2. Принцип работы 3. Структура записи в кэше 4. Виды промахов 5. Трансляция адресов 6. Иерархия кэшей в современных микропроцессорах 7. Реализации

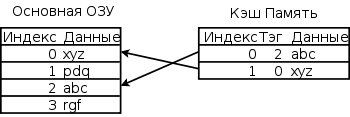

Диаграмма кэшей ЦПУ

Данный раздел описывает типичный кэш данных и некоторые виды кэшей инструкций; TLB может быть устроен сложнее, а кэш инструкций — проще. На диаграмме справа изображены основная и кэш память. Каждая строка — группа ячеек памяти содержит данные, организованные в кэш-линии. Размер каждой кэш-линии может различаться в разных процессорах, но для большинства x86-процессоров он составляет 64 байта. Размер кэш-линии обычно больше размера данных, к которому возможен доступ из одной машинной команды. Каждая группа данных в памяти размером в 1 кэш-линию имеет порядковый номер. Для основной памяти этот номер является адресом памяти с отброшенными младшими битами. В кэше каждой кэш-линии дополнительно ставится в соответствие тег, который является адресом продублированных в этой кэш-линии данных в основной памяти. При доступе процессора в память сначала производится проверка, хранит ли кэш запрашиваемые из памяти данные. Для этого производится сравнение адреса запроса со значениями всех тегов кэша, в которых эти данные могут хранится. Случай совпадения с тегом какой-либо кэш-линии называется попаданием в кэш, обратный же случай называется кэш промахом. Попадание в кэш позволяет процессору немедленно произвести чтение или запись данных в кэш-линии с совпавшем тегом. Отношение количества попаданий в кэш к общему количеству запросов к памяти называют hit rate, оно является мерой эффективности кэша для выбранного алгоритма или программы. В случае промаха, в кэше выделяется новая запись, в тег которой записывается адрес текущего запроса, а в саму кэш-линию — данные из памяти после их прочтения либо данные для записи в память. Промахи по чтению задерживают исполнение, поскольку они требуют запроса данных в более медленной основной памяти. Промахи по записи могут не давать задержку, поскольку записываемые данные сразу могут быть сохранены в кэше, а запись их в основную память можно произвести в фоновом режиме. Работа кэшей инструкций во многом похожа на вышеприведенный алгоритм работы кэша данных, но для инструкций выполняются только запросы на чтение. Кэш инструкций похож на кэш данных, но из него производится только чтение. Кэши инструкций и данных могут быть разделены для увеличения производительности или объединены для упрощения аппаратной реализации. Для добавления данных в кэш после кэш промаха может потребоваться вытеснение ранее записанных данных. Для выбора замещаемой линейки используется эвристика, называемая replacement policy. Основной проблемой алгоритма является предсказание, какая линейка вероятнее всего не потребуется для последующих операций. Качественные предсказания сложны, и аппаратные кэши используют простые правила, такие как LRU. Пометка некоторых областей памяти как некэшируемых улучшает производительность за счет запрета кэширования редко используемых данных. Промахи для такой памяти не создают копию данных в кэше. При записи данных в кэш, должен существовать определенный момент времени, когда они будут записаны в основную память. Это время контролируется политикой write policy. Для кэшей write-through, любая запись в кэш приводит к немедленной записи в память. Другой тип кэшей, write-back откладывает запись на более позднее время. В таких кэшах отслеживается состояние кэш линеек еще не сброшенных в память. Запись в память производится при вытеснении подобной линейки из кэша. Таким образом, промах в write-back кэше может потребовать двух операций доступа в память, один для сброса состояния старой линейки и другой — для чтения новых данных. Существуют также смешанные политики. Кэш может быть write-through, но записи могут временно помещаться в очередь и объединяться друг с другом для уменьшения количества транзакций на шине. Данные в основной памяти могут изменяться не только процессором, но и периферией, использующей прямой доступ к памяти, или другими процессорами в многопроцессорной системе. Изменение данных приводит к устареванию их копии в кэше. В другом реализации, когда один процессор изменяет данные в кэше, копии этих данных в кэшах других процессоров будут помечены как stale. Для поддержания содержимого нескольких кэшей в актуальном состоянии используется специальный протокол кэш когерентности. Просмотров: 8145

|