|

|

|

Компьютеры - Intel P6 - Функциональные устройства01 июня 2011

Оглавление:

1. Intel P6

2. Функциональные устройства

3. Исполнение инструкции

4. Особенности архитектуры

5. Процессоры архитектуры P6

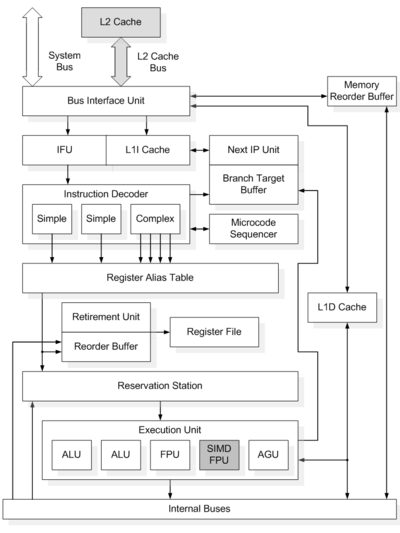

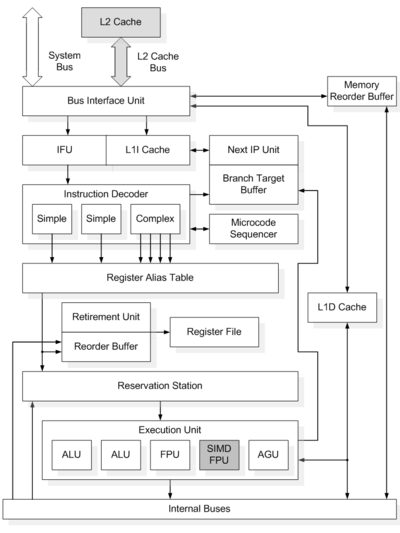

Функциональная схема процессора Pentium III на ядре Coppermine

Процессоры архитектуры P6 состоят из четырёх основных подсистем:

- Подсистема упорядоченной предварительной обработки — отвечает за выборку и декодирование инструкций в порядке, предусмотренном программой, и предсказывает переходы.

- Ядро исполнения с изменением последовательности — отвечает за исполнение микроопераций в оптимальном порядке и организует взаимодействие исполнительных устройств.

- Подсистема упорядоченного завершения — выдаёт результаты исполнения в порядке, предусмотренном программой.

- Подсистема памяти — обеспечивает взаимодействие процессора с оперативной памятью.

- Подсистема упорядоченной предварительной обработки

К устройствам этой подсистемы относятся:

- Модуль и буфер предсказания переходов — предсказывают переходы и хранят таблицу истории переходов. Для предсказания используются как динамический, так и статический методы. Последний используется в том случае, если динамическое предсказание невозможно.

- Декодер инструкций — преобразует CISC-инструкции x86 в последовательность RISC-микроопераций, исполняемых процессором. Включает два декодера простых инструкций, обрабатывающих команды, которые могут быть выполнены одной микрооперацией, и декодер сложных инструкций, обрабатывающего команды, для которых нужно несколько микроопераций.

- Планировщик последовательностей микроопераций — хранит последовательности микроопераций, используемые при декодировании сложных инструкций x86, требующих более четырёх микроопераций.

- Блок вычисления адреса следующей инструкции — вычисляет адрес инструкции, которая должна быть обработана следующей, на основании информации о прерываниях и таблицы переходов.

- Блок выборки инструкций — осуществляет выборку инструкций из памяти по адресам, подготовленным блоком вычисления адреса следующей инструкции.

Процессоры на ядре Tualatin дополнительно содержат блок предвыборки инструкций, который осуществляет предварительную выборку инструкций на основании таблицы переходов.

- Ядро исполнения с изменением последовательности

Исполнение с изменением последовательности, при котором меняется очерёдность исполнения инструкций, так, чтобы это не приводило к изменению результата, позволяет ускорить работу за счёт более оптимального распределения запросов к вспомогательным блокам и минимизации их простоев. К устройствам организации исполнения с изменением последовательности относятся:

- Таблица назначения регистров — задаёт соответствие между регистрами архитектуры x86/IA32 и внутренними регистрами, используемыми при исполнении микроопераций.

- Буфер переупорядочивания микроопераций — обеспечивает выполнение микроопераций в оптимальной с точки зрения производительности последовательности.

- Станция-резервуар — содержит инструкции, отправляемые на исполнительные устройства.

К исполнительным устройствам ядра относятся:

- Арифметическо-логические устройства, АЛУ — выполняют целочисленные операции.

- Блок арифметики с плавающей запятой — выполняет операции над числами с плавающей точкой. Процессоры Pentium III и выше имеют также блок, осуществляющий исполнение инструкций SSE.

- Блок генерации адресов — вычисляет адреса данных, используемых инструкциями, и формирует запросы к кешу для загрузки/выгрузки этих данных.

- Подсистема упорядоченного завершения

- Регистровый файл — хранит результаты операций.

- Буфер переупорядочивания памяти — управляет порядком записи данных в память для предотвращения записи неверных данных из-за изменения порядка выполнения инструкций.

- Блок завершения — выдаёт результаты исполнения инструкций в той последовательности, в которой они поступили на исполнение.

- Подсистема памяти

Объём L2 процессоров архитектуры P6

| Объём |

Процессоры |

| 128 |

Celeron, Pentium III |

| 256 |

Pentium Pro, Pentium III, Xeon |

| 512 |

Pentium Pro, Pentium II, Pentium III, Xeon |

| 1024 |

Pentium Pro, Xeon |

| 2048 |

Xeon |

Подсистема памяти осуществляет взаимодействие с оперативной памятью. К этой подсистеме относятся:

- Кэш первого уровня для данных — память с малым временем доступа объёмом 8 или 16 килобайт, предназначенная для хранения данных.

- Кэш первого уровня для инструкций — память с малым временем доступа объёмом 8 или 16 килобайт, предназначенная для хранения инструкций.

- Кэш второго уровня. Память с малым временем доступа объёмом 128, 256, 512, 1024 или 2048 килобайт. Ширина шины L2 составляет 64 или 256 бит. Процессоры Celeron на ядре Covington кэша второго уровня не имеют.

- Блок шинного интерфейса — управляет системной шиной.

Просмотров: 4562

|